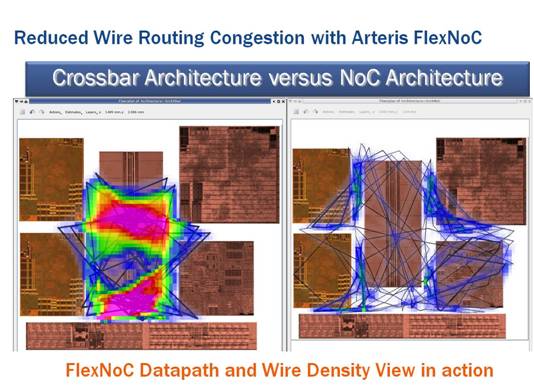

Congestion Driven Placement for VLSI Standard Cell Design Shawki Areibi and Zhen Yang School of Engineering, University of Guelph, Ontario, Canada December. - ppt download

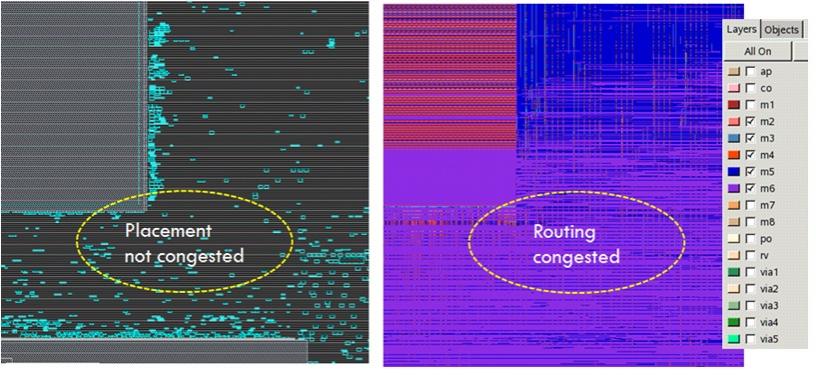

Routing Congestion too high' error at Global Routing step · Issue #173 · The-OpenROAD-Project/OpenROAD-flow-scripts · GitHub

Routing Congestion in VLSI Circuits: Estimation and Optimization (Integrated Circuits and Systems): Saxena, Prashant, Shelar, Rupesh S., Sapatnekar, Sachin: 9781846283536: Amazon.com: Books

Virtuoso: The Next Overture - Congestion Analysis with a New Perspective - Custom IC Design - Cadence Blogs - Cadence Community

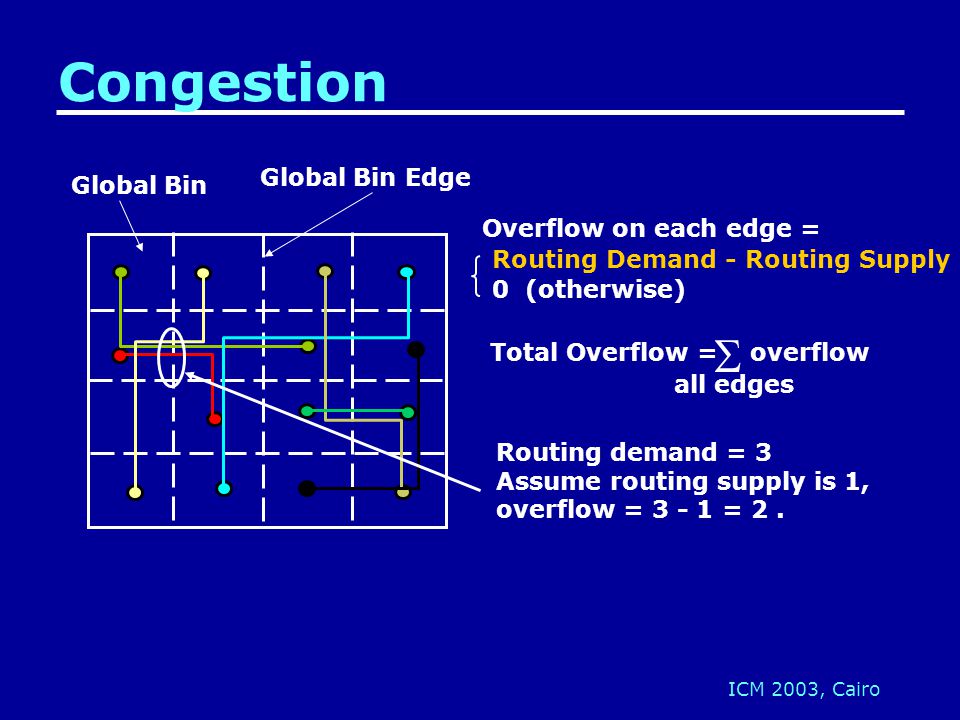

![PDF] Congestion analysis for global routing via integer programming | Semantic Scholar PDF] Congestion analysis for global routing via integer programming | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/44b2e47a979936ccd064dced312680a8074989da/2-Figure1-1.png)