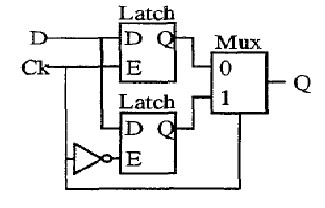

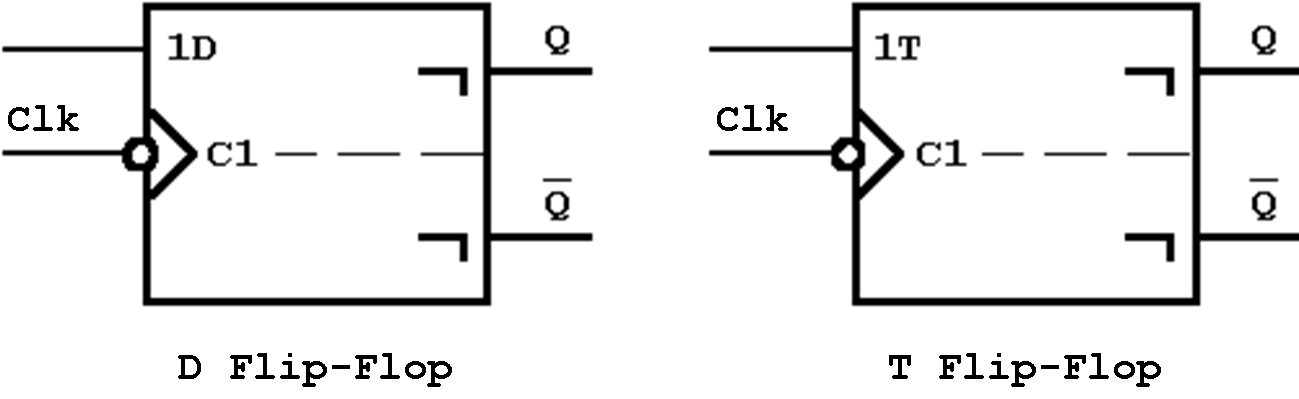

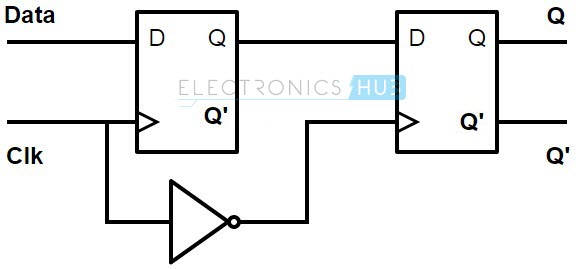

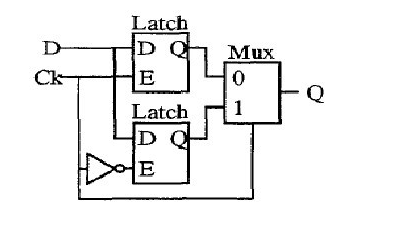

Dual edge sequential architecture capable of eliminating complete hold requirement from the test path

Dual edge sequential architecture capable of eliminating complete hold requirement from the test path

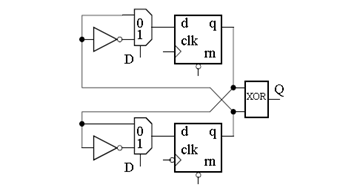

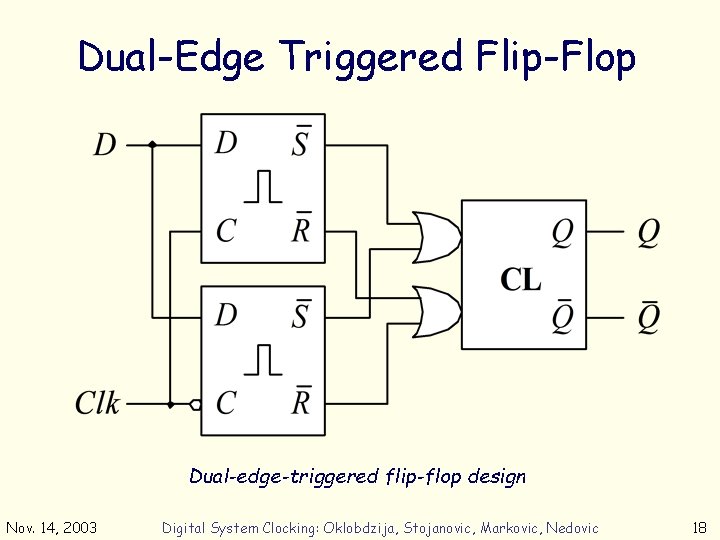

a) Conditional Precharage Double Edge-triggered Flip-Flop (b) Timing... | Download Scientific Diagram

Dynamic signal driving strategy based high speed and low powered dual edge triggered flip flop design used memory applications - ScienceDirect